#### About Analog Dialogue

Analog Dialogue is the free technical magazine of Analog Devices, Inc., published continuously for thirty-five years, starting in 1967. It discusses products, applications, technology, and techniques for analog, digital, and mixed-signal processing.

Volume 35 incorporates all articles published during 2001 in the Worldwide Web editions **www.analog.com/analogdialogue**—and more. All recent issues, starting with Volume 29, Number 2 (1995) have been archived on that website and can be accessed freely. Two special anniversary issues in the archives contain useful articles extracted from earlier editions, going all the way back to Volume 1, Number 1. This issue revisits two series that have proved popular in the recent quinquennium.

Analog Dialogue's objectives have always been to inform engineers, scientists, and electronic technicians about new ADI products and technologies and to help them understand and competently apply these products.

The frequent Web editions have at least three further objectives:

- To provide digests that alert readers to prereleased and newly available products.

- To provide a set of links to important and rapidly proliferating sources of information and activity fermenting within the ADI website (www.analog.com).

- To listen to reader suggestions and provide answers to their questions.

Thus, *Analog Dialogue* is more than a magazine; its links and tendrils to all parts of our external website make its bookmark a favorite "high-pass-filtered" point of entry to the **analog.com** site—the virtual world of Analog Devices.

Our hope is that readers will think of ADI publications as "Great Stuff" and will consider the *Analog Dialogue* bookmark a favorite alternative path to answer the question, "What's new in technology at ADI?"

Welcome! Read and enjoy! We encourage your feedback!

Dan Sheingold

dan.sheingold@analog.com

Editor, Analog Dialogue

Dan Sheingell

#### IN THIS ISSUE

#### Analog Dialogue Volume 35, 2001

This annual issue of *Analog Dialogue* contains reprints of all the articles published in the on-line editions during 2001. As a special bonus, in celebration of our 35th year in print, we are adding reprints of two collections that have proven popular during the past five years: Dave Robertson's five-part 1996–1997 series, "Selecting Mixed-Signal Components for Digital Communication Systems," and all installments of the "Ask The Applications Engineer" series, published on line (and in print) since the 30th anniversary collection in 1996. (You can find that publication in our *Analog Dialogue* on-line Archives.)

|                                                                                            | Page |

|--------------------------------------------------------------------------------------------|------|

| Editor's Notes: Authors, New Fellows                                                       | 2    |

| Accurate Gain/Phase Measurement at Radio Frequencies up to 2.5 GHz (AD8302)                | 5    |

| High Performance Narrowband Receiver Design Simplified by                                  |      |

| IF Digitizing Subsystem in LQFP (AD9870)                                                   | 9    |

| Mixed-Signal Front End (MxFE) for Broadband Digital Set-Top Boxes (AD9873)                 | 13   |

| Design a Direct 6-GHz Local Oscillator with a Wideband Integer-N PLL Synthesizer (ADF4106) | 17   |

| Winning the Battle Against Latch-up in CMOS Analog Switches                                | 21   |

| Avoiding Op Amp Instability Problems In Single-Supply Applications                         | 24   |

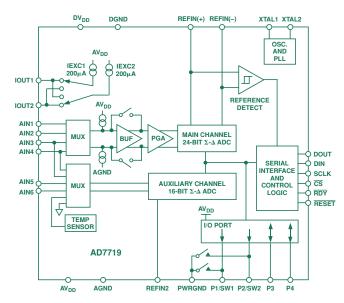

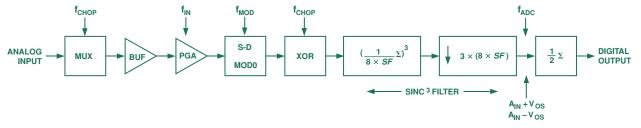

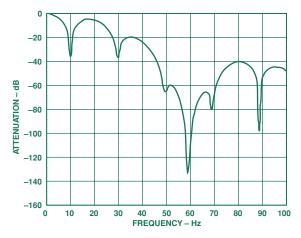

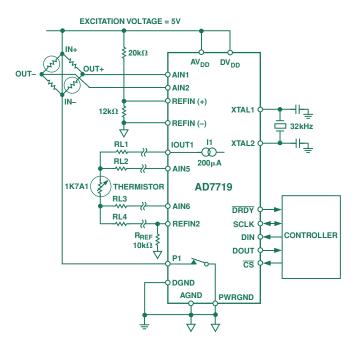

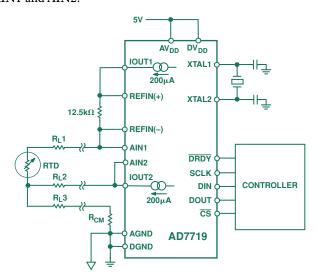

| Improved Data Acquisition Using a New Monolithic Dual-ADC Front End (AD7719)               | 27   |

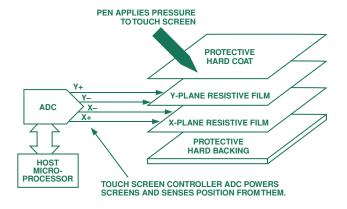

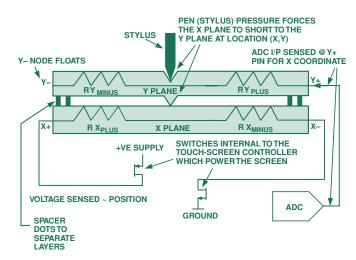

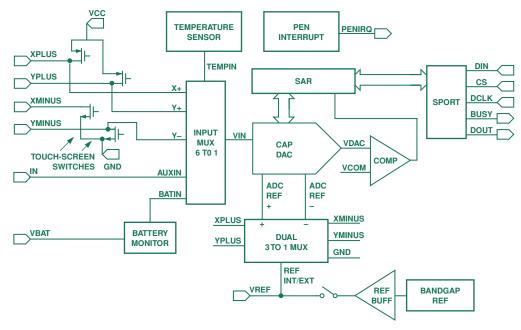

| The PDA Challenge—Met by the AD7873 Resistive-Touch-Screen Controller ADC                  | 30   |

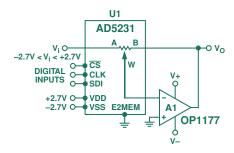

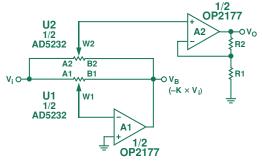

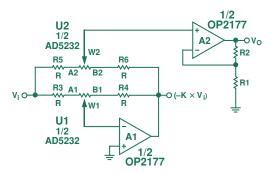

| Versatile Programmable Amplifiers Use Digital Potentiometers with Nonvolatile Memory       | 35   |

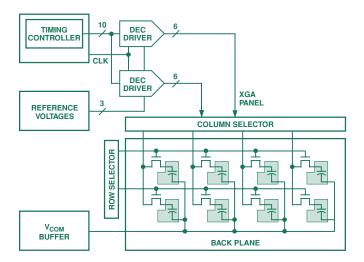

| Advanced LCD Driver Lowers Cost of High Performance Data Projectors (AD8380)               | 37   |

| Sensing, Analyzing, and Acting in the First Moments of an Earthquake                       | 41   |

| A Useful Role for the ADXL202 Dual-Axis Accelerometer in                                   |      |

| Speedometer-Independent Car-Navigation Systems                                             | 44   |

| 35TH ANNIVERSARY BONUS MATERIAL                                                            |      |

| Ask the Applications Engineer                                                              |      |

| 24: Resistance                                                                             | 47   |

| 25: Op Amps Driving Capacitive Loads                                                       |      |

| 26: Switches and Multiplexers                                                              |      |

| 27: Signal Corruption in Industrial Measurement                                            |      |

| 28: Logarithmic Amplifiers Explained                                                       |      |

| 29: Accelerometers—Fantasy and Reality                                                     | 63   |

| Selecting Mixed-Signal Components for Digital Communication Systems                        |      |

| I: An Introduction                                                                         |      |

| II: Digital Modulation Schemes                                                             |      |

| III: Sharing the Channel                                                                   |      |

| IV: Receiver Architecture Considerations                                                   |      |

| V: Aliases, Images, and Spurs                                                              | 77   |

#### **Editor's Notes**

At the close of 2001, we celebrate the completion of *Analog Dialogue*'s 35th year in print—and the third year of its electronic version. This season also marks the beginning of the undersigned's 34th year at Analog Devices as Editor of this journal—and his 53rd year of advocating analog technology. In the early days, at Philbrick, this featured K3 Analog Computor (*sic*) building

blocks. But they would soon be overshadowed in fame and cannibalized in fortune by the yet smaller, still undifferentiated, analog building block that lurked within, dreaming of an identity.

It materialized in 1952 as Philbrick's versatile and ubiquitous K2-W plug-in Differential Operational Amplifier, which celebrates the jubilee of its birth in 2002. The K2-W, with its two 12AX7 tubes plugged in at the top, was the harbinger of a new era of compact precision at low cost in modular measurement, control, and much else. By plugging into an octal tube socket in the same way as a tube (and in the same way that the later ICs plugged into transistor-type sockets), this "smart tube" could also be considered a forerunner of the integrated circuit. At the heart of circuits and modules that perform analog computing, it could even be said that op amps resulted in the transformation of analog computers into components—in the same way that microprocessors would later turn digital computers into components.

OK. Enough of analogy! Let's get on with Analog.

#### **AUTHORS**

John Cowles (page 5) works at ADI Northwest Labs in Beaverton, Oregon, designing RF-IF products for the communications market. He received a PhD in EE from the University of Michigan in 1994. Before joining ADI in 1998, he worked at TRW, in Redondo Beach, CA, on high-speed GaAs and InP technologies. At ADI, he designed the AD8302, which was nominated for Product of the Year by

both *Electronic Products* and *EDN* magazines. He has over 50 technical publications on high-speed devices and circuits.

Mike Curtin (page 17) is the applications manager for RF products in Ireland. Mike graduated from the University of Limerick with a BSc in Electronic Engineering. He worked in various local companies before joining Analog Devices in 1983 as an Applications Engineer. He has provided technical support for a wide variety of Limerick-developed products, including high-speed ADCs, sigma-delta ADCs,

and DACs, an activity interrupted by a two-year assignment as a field applications engineer in the U.S. In his spare time, he listens to music and enjoys a game of snooker or indoor football.

Joe DiPilato (pages 9, 13), is the product-line manager for communication-specific integrated products within ADI's High-Speed Converter (HSC) group. Since joining ADI in 1987, he has been involved with industrial, instrumentation, and communication-focused products and for the last eight years, HSC standard- and communication-specific

products, including TxDAC<sup>®</sup> and MxFE<sup>™</sup> brands. He has authored numerous articles. Joe has a BSEE from Worcester Polytechnic Institute (1982) and an MBA from Anna Maria College (1984). He is active in his church, and enjoys swimming and quality beach time with his wife Lisa and son Nicholas.

Zoltan Frasch (page 37) is principal applications engineer for ADI's Display-Drive Electronics group. He earned his BSEE from the University of Toronto, Canada, in 1976 and joined ADI in 1999.

Barrie Gilbert (page 5), the first ADI Fellow, has "spent a lifetime in the pursuit of analog elegance." He joined Analog Devices in 1972, was appointed ADI Fellow in 1979, and manages the Northwest Labs in Beaverton, Oregon. Barrie was born in Bournemouth, England, in 1937. Before joining ADI, he worked with first-generation transistors at SRDE in 1954, and at

Mullard, Ltd.; later at Tektronix and Plessey Research Labs. Barrie is an IEEE Fellow (1984) and has received numerous awards. He has some 50 issued patents, has authored about 40 papers, is co-author of several books, and is a reviewer for several journals. He was awarded an Honorary Doctorate of Engineering from Oregon State University in 1997.

Paul Hendriks (page 9) is a senior applications engineer for ADI's Standard Linear Products Division (Wilmington, MA). He has been working in the High-Speed Converter product group for the past 8 years, focusing on the use of high-speed converters in communication applications. Since joining ADI in 1989, he has authored numerous articles, design ideas, and product

data sheets. Paul received a BSEE in 1986 from McGill University.

Paul Kearney (page 30) is a design engineer in ADI's Precision-Converter product line, in Limerick, Ireland. He was graduated with a BE in Electrical Engineering from University College Cork, Ireland, and joined ADI immediately thereafter, in 1990. Before his present assignment, in 1998, he worked as a product engineer.

Martin Kessler (page 13) first encountered ADI in 1990, as a coop student in Munich, Germany. In 1994, he joined the company full-time, providing application support for all product lines. Subsequently, Martin moved to ADI Wilmington, where he focuses his efforts on digital communication-specific ICs and mixed-signal front ends. Hobbies include skiing, hiking, backpacking, and playing the guitar.

Charles ("Chuck") Kitchin (page 24) is a hardware applications engineer at ADI in Wilmington, MA. His main responsibilities include writing technical publications and developing new applications circuits. He has published over 70 technical articles, three books, and a large number of application notes. Chuck graduated with an ASET from Wentworth

Institute, in Boston, and then continued studying electrical engineering at the University of Lowell. His avocations include astronomy, amateur radio, and oil painting.

Alan Li (page 35) is an applications engineer in the General-Purpose Converter and Reference product line of the Precision Converter Division. He has a BSEE from the Florida International University and is currently pursuing a graduate degree at San Jose State University. He has also worked at National Semiconductor and Fairchild Semiconductor, focusing on power-

electronics applications. His leisure, activities include playing soccer and listening to music.

Iuri Mehr (page 13) is a design engineer for communications-specific products in ADI's High-Speed Converter Group, Wilmington, MA. He received the MSEE degree from Washington State University in 1994. After a two-year stint as Design Engineer for Crystal Semiconductor, he joined ADI in 1996, in the Standard Products group. In 1997, he joined the

High-Speed Converter group. He serves as an Associate Editor for *IEEE Transactions on Circuits and Systems II*.

Albert O'Grady (page 27) is a staff applications engineer at ADI's facility in Limerick, Ireland, providing applications support for general-purpose digital-to-analog converters (DACs) and high-resolution, low-bandwidth, sigma-delta analog-to-digital converters (ADCs). Albert holds a BEng from the University of Limerick. In his spare time, Albert

enjoys reading and plays badminton and tennis.

Giuseppe Olivadoti (page 41) is the technical marketing specialist for the DSP Development Tools product line. He holds a BS in Electrical Engineering with a concentration in Computer Engineering from Northeastern University.

Catherine Redmond (page 21) is an applications engineer at ADI's facility in Limerick, Ireland, providing applications support for general-purpose D/A converters and Switch/Multiplexer products. Catherine holds a BEng from Cork Institute of Technology and joined ADI in 1997. Her interests include listening to music, reading, and travelling.

Richard Schreier (page 9) is a design engineer in ADI's High-Speed Converters group, in Wilmington, MA. He received a PhD degree from the University of Toronto in 1991. Before joining ADI, he was an Assistant Professor at Oregon State University in Corvallis, Oregon, from 1991 to 1997. Richard is a coedi-tor of a 1997 IEEE Press book on deltasigma converters; he also authored a

freeware Matlab toolbox for the high-level design and simulation of delta-sigma modulators.

Peter Shih (page 44) is an applications engineer with the Central Applications group in Wilmington, MA, working closely with product-line applications engineers to provide customer support for linear products. He joined ADI in May 2000, after graduating from Tufts University with a BSEE. His interests include playing volleyball, traveling, and eating!

Ed Spence (page 37) is product manager of ADI's display-drive electronics strategy, based in Wilmington, MA. He received a BSEE from the University of Lowell, MA. Ed joined ADI in 1989.

Harvey Weinberg (page 44) is an applications engineer for ADI's Micromachined Products division in Cambridge, MA. He has a BEng in Electrical Engineering from Concordia University, Montreal, Canada. For nine years, prior to working as an applications engineer, he designed analog- and microcontroller-based instrumentation for the process-control industry.

#### **NEW FELLOWS**

We are pleased to note the introduction of *four* new Fellows at our 2001 General Technical Conference. Fellow, at Analog Devices (ADI), represents the highest level of achievement that a technical contributor can attain, on a par with Vice President. The criteria for promotion to Fellow are very demanding. Fellows will have earned universal respect and recognition from the technical community for unusual talent and identifiable innovation at the state of the art. Their creative technical contributions in product or process technology, or software, will have led to commercial success with a major impact on the company's net revenues and earnings.

Attributes include roles as mentor, consultant, entrepreneur, organizational bridge, teacher, and ambassador. Fellows must also be effective as leaders and members of teams—and in perceiving customer needs. In the year 2001, the unprecedented number of four outstanding individuals—Denis Doyle, Paul Ferguson, Josh Kablotsky, and Larry Singer—were identified as having the rare combination of technical abilities, accomplishments, and personal qualities to qualify them to enhance our existing roster of Fellows: Bob Adams (1999), Woody Beckford (1997), Derek Bowers (1991), Paul Brokaw (1979), Lew Counts (1983), Barrie Gilbert (1979), Roy Gosser (1998), Bill Hunt (1998), Jody Lapham (1988), Chris Mangelsdorf (1998), Jack Memishian (1980), Doug Mercer (1995), Frank Murden (1999), Mohammad Nasser (1993), Wyn Palmer (1991), Carl Roberts (1992), Paul Ruggerio (1994), Brad Scharf (1993), David Smart (2000), Jake Steigerwald (1999), Mike Timko (1982), Bob Tsang (1988), Mike Tuthill (1988), Jim Wilson (1993), and Scott Wurcer (1996).

#### **DENIS DOYLE**

Denis is a major contributor to process development and operations at ADI's Limerick (Ireland) wafer fab. His principal contributions have been in the evolution of BiCMOS processes from 1-µm to 0.35-µm feature size. He has also worked on other projects, ranging from EPROMs and ESD to process transfers between ADI and our foundries.

Denis Doyle received his BE (Elect) from University College, Cork, Ireland, in 1985, followed by the MEngSc and PhD—for his work in small-geometry bipolar devices at the National Microelectronics Research Centre (NMRC), in Cork, Ireland. In 1991, he joined the Process Development group at ADI, Limerick, where he has since worked on and led process developments. Denis's current project is on the development of a 0.6-µm, 30-V CMOS/BiCMOS process.

#### **PAUL FERGUSON**

Paul is an inventive circuit designer who has contributed heavily in the field of switched-capacitor circuits and higher-order sigma-delta ADCs and DACs. He was instrumental in the development of new inventions and technologies that led to the emergence of ADI as the leader in the PC business audio segment. Among these are new

ideas for offset calibration, which led to a reduction in "speaker pop" phenomena, once common throughout audio applications. He was also a pioneer in standard-cell layout and novel higher-order sigma-delta loop architectures at ADI.

Besides his contributions as an inventor and designer, he also excels as a teacher, mentor, and team builder, has developed strong relationships with universities, has delivered many technical papers and lectures, and has served a key role in recruiting promising graduates. He has an AB from Dartmouth College and an SM in EE from MIT—and is in pursuit of his PhD from Oregon State University. He holds 16 patents and is currently a key player in mixed-signal development for ADI's RF and wireless systems, including the SoftFone<sup>TM</sup> and Othello<sup>TM</sup> chipsets. Paul lives in North Andover, MA, with his wife, Amy, and their three children.

#### **JOSH KABLOTSKY**

Joining the Development Tools group in 1990, Josh has contributed heavily to DSP software development and created numerous software development methodologies and tools that are now in daily use throughout the company. He has developed DSP software for successful ADI products in diverse communications and

computer segments—and is now focused on DSP-based video and image processing. He has been responsible for remote-access and voice-over networks businesses, consulted on processor architectures, and has been ADI's primary contact to organizations such as ITU-T and TIA.

He has contributed to development in many product areas, including DSP answering-machine software, voice compression and tone detection, acoustic echo cancellation, modem development, state-machine design, and remote data gathering. Through application by others of his development methodologies, he has also contributed indirectly to a much wider universe, including digital still cameras, color laser printers, 3G wireless infrastructure, wireless terminals, and IADs. He has a BSEE from Cornell University, and currently lives in Sharon, MA, with his wife, Deborah.

#### **LARRY SINGER**

Larry is most recently the lead A/D converter designer for the High-Speed Converter Standard Products group in Wilmington, MA. He is a graduate of MIT, with SB (1985) and SM (1987) degrees in EE. He joined ADI upon graduation, after being recruited by Fellow-to-be Paul Ferguson. Since then he has developed many of ADI's

converters that join high speed and high resolution, including both successive-approximation and high-speed pipelined types.

Early in his career, he solved challenging problems in the design of practical 12- and 14-bit ADCs in bipolar-CMOS (BiCMOS), that used laser-trimmed thin-film-on-chip resistors. He then moved on to moderate resolution (to 12 bits) video (20-MSPS) converters, designing pipelined converters in high-speed FLAMOS, an advanced bipolar-CMOS process—with laser-trimmed resistors. Since then his major contributions have been in innovative CMOS designs, pushing the boundaries of capacitor matching and segmentation, and showing that performance up to 14 bits could be realized without calibration. With his efforts, CMOS devices are closing the speed and dynamic-performance gap with bipolar and BiCMOS devices. Larry is married, has two children, and enjoys drumming and playing volleyball.

## Accurate Gain/Phase Measurement at Radio Frequencies up to 2.5 GHz

by John Cowles (john.cowles@analog.com) and Barrie Gilbert (barrie.gilbert@analog.com)

#### **INTRODUCTION**

#### **Measuring Signals**

Electronic circuits fall into two broad categories—those that *process* and transform signals and those that *measure* signals. Their functions are often combined, as in the IF section of a receiver—which processes the signal (by amplification and demodulation), and also delivers an indication of received signal-strength (the RSSI function), a slowly-varying voltage that may be displayed and/or used for automatic control of variables such as gain and frequency (AGC and AFC).

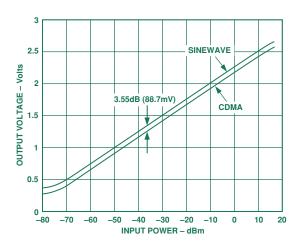

Circuits that measure RF signal strength, whose fundamental metric is power, are generally called detectors, but only a thermopile (bolometer) measures this quantity directly. Integrated-circuit detectors invariably operate on a voltage sample of the signal to be measured. Circuits of this class are classified by the type of signal transformation they provide. In 1976, Analog Devices supplied the first monolithic "true-rms" detectors for use at moderate frequencies. Now this product line includes devices, such as the AD8361, that have extended this capability to the microwave domain. The accurate determination of signal power, independent of its waveshape (stated otherwise, its probability density function) is important in modern communications systems such as CDMA. Unlike thermal detectors, these true-rms detectors use analog computation to directly implement the relevant equations—at gigahertz frequencies.

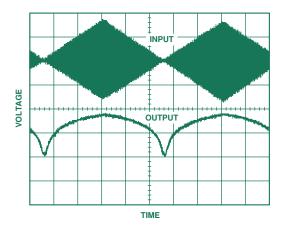

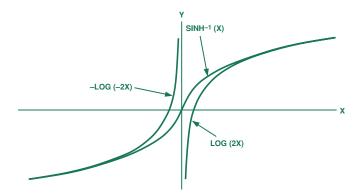

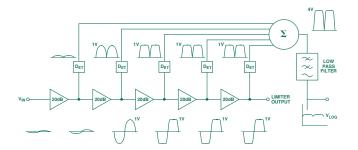

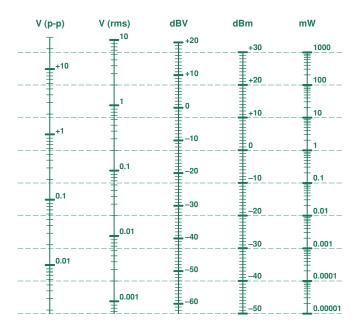

Another valuable type of RF detector (also using computation) is the demodulating logarithmic amplifier. As the name suggests, it amplifies the signal, which allows devices of this class to measure small signals, and it demodulates the alternating RF waveform to a slowly-varying "quasi-dc" output. However, unlike the rms detectors, whose output is proportional to the root-mean-squared value of the input voltage, logarithmic detectors deliver an output proportional to the decibel value of the signal level, referenced to a fixed voltage,  $V_{INT}$  (defined below). The output, usually a voltage, may be interpreted in terms of either voltage or power, simply by using a different value for a scaling parameter called the "slope."

For RF log amps, it is necessary to use voltage metrics for all the signal and scaling parameters. To define the input level, we will use dBV (here meaning decibels relative to 1 V rms) rather than refer to "power," in dBm (decibels relative to 1 mW). This is unambiguous, independent of the choice of impedance at the input interface, and appropriate for an IC detector. For example, 0 dBV corresponds to a sine wave of 2.83-V p-p amplitude; similarly, –60 dBV refers to a 2.83-mV p-p sine wave.

The operation of these RF logarithmic detectors conforms to a function like this:

$$V_{OUT} = V_{SLP} \log(V_{SIG}/V_{INT}) \tag{1}$$

If base-10 logarithms are chosen  $[\log_{10}(10) = 1 \text{ decade}]$ , with decibels in mind, the slope voltage,  $V_{SLP}$ , can be viewed in terms of "volts-per-decade" in the scaling of the log of the voltage ratio. Since there are 20 decibels in a decade, the corresponding "volts/dB" is just one-twentieth of this voltage. Thus, for a  $V_{SLP}$  of 400 mV/decade, the slope can also be expressed as 20 mV/dB. The second scaling parameter, called the "intercept,"  $V_{INT}$ , is the input voltage at which the log argument is unity. At this voltage, independent of choice of base, the output would be zero, since  $\log(1) = 0$ . In practice, the finite available gain in an RF log amp, the presence of noise, and other practical limitations result in a value for  $V_{INT}$  that is an *extrapolated* value, typically only a few microvolts, and fixed by the design.

A question then arises as to the precise interpretation of what  $V_{INT}$  represents. Is this quantity "volts dc," or perhaps "volts rms"? Or is it some other metric, such as a simple average value, or the peak value? For measurements of ratios from one level to another, the value of  $V_{INT}$  is unimportant. However, where it is required to determine the *absolute* level of  $V_{SIG}$ , the measurement accuracy depends directly on the value of  $V_{INT}$  in just the same way as a reference voltage in, say, a DVM.

A close study of RF logarithmic amplifiers, which use the technique known as "progressive compression," shows another effect not encountered in classical log amp practice, namely, that the effective value of  $V_{INT}$  strongly depends on the *waveform* of the input signal. For that reason, we choose to define  $V_{INT}$  for a sinusoidal input, and then provide conversion factors for various other waveforms.

In practice, the control of  $V_{INT}$  in an untrimmed production IC cannot be as accurate as is often needed in precision RF metrication. Laser trimming, first used for an RF log amp in the AD640/641, and more recently in products such as the AD8306, can provide very accurate calibration, using a sine-wave input during calibration. However, while the use of the appropriate conversion factor for a known waveform can maintain good accuracy, there remains the basic problem of waveform-dependence. This poses a problem in contemporary systems where the waveform is both unknown and can vary rapidly.

#### Measurement of Signal Ratios to 2.5 GHz

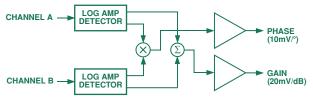

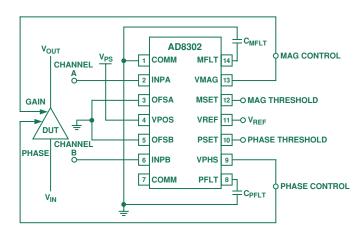

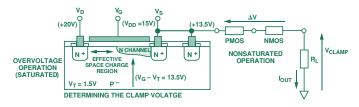

This problem has been addressed, in the AD8302, by the use of two identical log amps integrated in monolithic form, as shown in Figure 1. Each channel is capable of measuring signals over a 60-dB range, from very low frequencies up to 2.5 GHz. The defining function for the *amplitude* ("gain") output is

$$V_{MAG} = V_{SLP} \log \left( V_A / V_B \right) + V_{CP} \tag{2}$$

where  $V_A$  and  $V_B$  are two independent signals, applied to the two identical input ports of the AD8302, and  $V_{CP}$  is the center-point, defined as the value of the output,  $V_{MAG}$ , for a level difference of 0 dB. ( $V_{SLP}$  and  $V_{CP}$  are design choices, made with ease-of-use in mind; both are traceable to a band-gap reference).

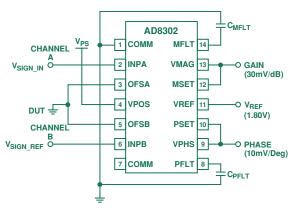

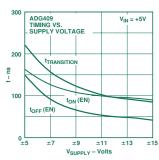

Figure 1. The AD8302 comprises a pair of accurately matched log amps and a high-frequency phase detector.

The customary fixed intercept of Equation 1, is eliminated in the AD8302 by taking the difference of the outputs of the two separate log amps. This key step computes the log of the ratio  $(V_A/V_B)\times(V_{INTB}/V_{INTA})$ ; and, since the log amps are identical, the second term is very accurately unity, independently of temperature, supply voltage, and numerous production variances.

This elegant elimination of a fixed intercept results in a highly accurate measurement of signal level, in many applications. The primary limitation to the accuracy of the log argument is now the matching of the two co-integrated channels. This novel "C" structure<sup>2</sup> opens up many measurement possibilities that would otherwise require the use of two distinct log amps, with their inherent differences in slope and intercept calibration. The AD8302 is the first IC to permit the *direct measurement of ac signal ratios*. This unique capability for measuring gain/loss and the relative phase (see below) between two signal ports, over a very wide range of frequencies, will be of value in many other applications.

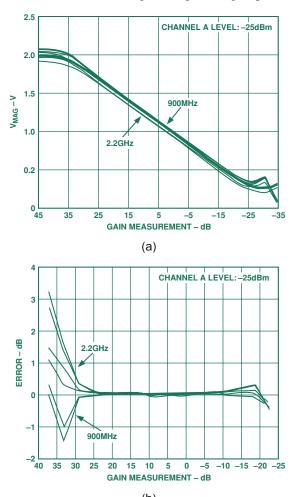

Figure 2 illustrates the output voltage variation as a function of signal ratio (which, for example, may correspond to the *gain or loss* of a channel being monitored) at frequencies ranging from 900 MHz to 2.2 GHz. The signal level presented to Channel B is fixed while that at Channel A is varied from –30 dB to +30 dB relative to Channel B. The output,  $V_{MAG}$ , demonstrates the precise slope,  $V_{SLP}$ , of 20 mV/dB and a center-point,  $V_{CP}$ , of 900 mV. The very small deviation from an ideal logarithmic law (Figure 2b) demonstrates the value of using co-integrated log amps.

Figure 2. Measurements of signal-level ratios (a) exhibit errors (b) of less than 0.2 dB up to high frequencies.

#### **Measurement of Relative Phase to 2.5 GHz**

The AD8302 can also measure the *phase difference* between two signals, from low frequencies up to 2.5 GHz. Each of the individual log amps generates a "hard-limited" output at its final stage. These signals are applied to the two inputs of a novel multiplier-style phase detector having exact symmetry with regard to its two inputs and a  $180^{\circ}$  range. The phase output,  $V_{PHS}$ , is given by,

$$V_{PHS} = \pm V_{\Phi} (\Phi - 90^{\circ}) + V_{CP}$$

(3)

where  $V_{\Phi}$  is the scaling voltage for the phase output and  $\Phi$  is the phase difference between the two inputs. The choice of sign depends on which two quadrants constitute the  $180^{\circ}$  phase interval. With the inclusion of this feature, the AD8302 becomes a "network analyzer on a chip."

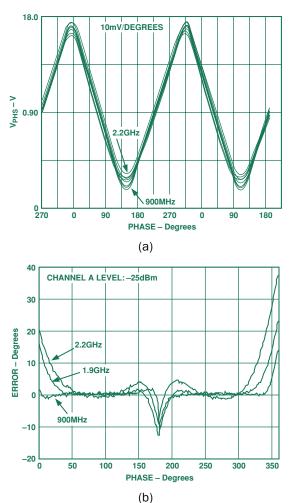

Figure 3 illustrates phase measurement at 900 MHz, 1.9 GHz, and 2.2 GHz. Here, the phase difference was generated as a "slip," by slightly offsetting the two input frequencies and allowing the angle to accumulate. The slope of the  $V_{PHS}$  output is 10 mV/°C, centered at a  $V_{CP}$  of 900 mV. The alternating sign of the slope is apparent as the phase slips through 180° intervals. Figure 3b shows the measurement error. The rapid increase in error near 0° and 180° is due mainly to dead-zones caused by the finite rise and fall times of the hard-limited signals. The unique ability of the AD8302 to accurately measure phase at these frequencies is a result of the excellent balance of its two tightly-integrated log amps.

Figure 3. The phase measurement (a) exhibits low errors (b) over wide angular ranges and up to high frequencies.

#### Using the AD8302

These new capabilities for measuring gain/loss and the relative phase between two signal ports will be of value in many RF and IF applications. The functionality, versatility, and compact form-factor of this "network analyzer on a chip" are ideally suited for in-situ diagnostics and monitoring of system parameters and for feedback and feed-forward linearization and control of subsystems. These are a few applications of the AD8302.

The measurement of absolute signal level is now possible using a known ac reference. As shown in Figure 4, the reference signal applied to Channel B creates an effective intercept of value  $V_B$ . When the two signals have similar waveforms, the measurement can be very accurate. Even the error due to uncertainty in the slope voltage can be minimized (eliminated, in principle) if one can ensure that the two inputs are close-to-equal in amplitude. This will often be a simple matter to arrange, using an attenuator pad on the larger signal to position the ratio  $V_A/V_B$  close to unity. Centering techniques are valuable when the highest accuracy is needed or where very large dynamic ranges must be handled.

Figure 4. Absolute measurements of signal level using an AC reference on Channel B as the intercept for Channel A.

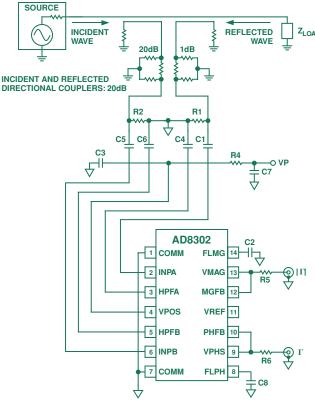

The most useful application of the AD8302 is in monitoring and reporting the gain or loss of a functional block or subsystem. In the example shown in Figure 5, samples of the input and output signals of a 500-MHz IF amplifier with a nominal gain of 20 dB are monitored. By using attenuators and couplers, the two signals are conditioned to be of the same general magnitude. The gain response shows the mid-scale low frequency value, which corresponds to a 20-dB level difference at the amplifier and a 3dB bandwidth of approximately 500 MHz. The functional block in this example could have been a frequency-translation device, such as a mixer. In that case, the two inputs would be at different frequencies, and the measured quantity would be the conversion gain. Since the waveforms remain similar, that source of error is again eliminated. However, when the input frequencies differ greatly, a systematic offset may occur due to inequalities in the impedance match and the frequency dependence of the scaling of the two log amps in the gigahertz region.

In many communication systems, there is an unpredictable load presented to an external interface port. Variations in this load can

Figure 5. The AD8302 monitoring the frequency response of an amplifier under test and reporting the gain.

COMM

4 VPOS

5 HPFB

6 INPB

VREF

PHFB

VPHS

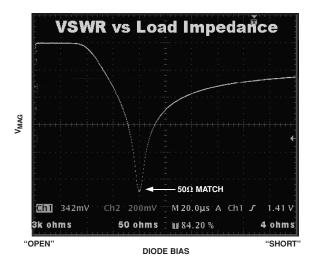

PHASE

lead to changes in system performance, or even to catastrophic failure in extreme cases. It is of great value to provide the means of monitoring the load impedance—or reflection coefficient in RF terms—without perturbing it. In Figure 6, the AD8302 is configured to measure the reflection coefficient of an arbitrary load which, in this case, is a PIN-diode whose bias is swept to change its impedance. The notch in the response curve represents a near-match to the 50- $\Omega$  characteristic line impedance, where the reflected signal is almost zero.

<sup>0.90</sup> 100mV VMAG 100MHz 1.00 V Ch2 60.0mV M10.0ms A Ch1 1 4.20 V m→▼ n nnnnn s 300MHz 1.3GHz FREQUENCY SOURCE 20dB Z<sub>LOAD</sub> 0dB 20dB INCIDENT AND REFLECTED **DIRECTIONAL COUPLERS: 20dB** R1 R2 AD8302 сомм INPA 2 MGFB 3

$<sup>^1\</sup>mathrm{A}$  detailed description of the theory of operation of log amps can be found in the AD640 data sheet.

<sup>&</sup>lt;sup>2</sup>Patent pending.

Figure 6. The AD8302 monitors the reflection coefficient of a load—a PIN diode whose impedance is manipulated by its bias.

#### **Versatility and Ease of Use**

The AD8302 offers several other modes of operation, the result of careful planning and the fundamentally versatile nature of this unusual structure. The previous examples have demonstrated the AD8302 in its typical *measurement* mode, where the  $V_{MAG}$  and  $V_{PHS}$  outputs report the signal level and phase difference between its inputs. However, the built-in scaling and center-points of the transfer functions can be adjusted using external resistors and the 1.80-V internal reference provided at the VREF pin.

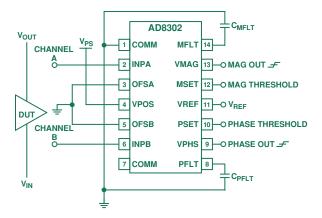

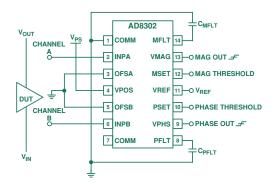

By disconnecting the output pins from the feedback pins, MSET and PSET, a gain- and phase-comparator is realized, as shown in Figure 7. Here, the  $V_{MAG}$  and  $V_{PHS}$  outputs toggle between 0 V and the maximum output voltage of 1.8 V, depending on whether the signal level and phase difference are greater than or less than the thresholds presented to the MSET and PSET pins.

Figure 7. The AD8302, configured as a gain- and phase-comparator with controllable thresholds.

In the *controller* mode, shown in Figure 8, the VMAG and VPHS pins drive gain/phase-adjusters that are included in the signal chain being monitored so as to servo the overall gain and phase of the system toward the desired set-points presented to the MSET and PSET pins.

Figure 8. The AD8302 in a control loop that drives the gain and phase of a DUT towards prescribed set-points.

The AD8302 has a broad frequency range at its inputs, ranging from arbitrarily low frequencies (even audio!) up to 2.5 GHz. The wide dynamic range of the log amps accommodates not only large changes in relative signal level but also variations in the absolute levels. The output quantities representing the amplitude and phase difference have a maximum small-signal envelope bandwidth of 30 MHz; this can optionally be reduced by adding external filter capacitors.

The AD8302 provides this powerful computational function for the first time in monolithic form using an advanced bipolar process. The excellent log-amp matching, high-frequency capability, and precise scaling of gain and phase measurement, all in a small footprint, open up new opportunities for *in-situ* monitoring and controlling of RF and IF systems in a noninvasive fashion. Operation from 2.7-V to 5.5-V supply voltages is provided at a current of only 20 mA. The product is available in a 14-pin TSSOP package.

#### **ACKNOWLEDGMENTS**

The authors would like to recognize the tireless efforts of Tom Kelly and Shirine Eslamdoust in product engineering, and Ron Simonson and Rick Cory for applications development.

## High Performance Narrowband Receiver Design Simplified by IF Digitizing Subsystem in LQFP

By Paul Hendriks, Richard Schreier, and Joe DiPilato (paul.hendricks@analog.com; richard.schreier@analog.com; joe.dipilato@analog.com)

#### **INTRODUCTION**

Mobile radios are used for public safety and emergency services—police, fire and ambulances—as well as for private services such as fleet management. Increasingly, in order to provide enhanced services, along with improved spectral efficiency and coverage, the design of these radios has moved from traditional analog-based modulation schemes, such as FM and PM, to digital modulation approaches.

Receivers for these radios must be capable of accurately digitizing a low-level, high-frequency signal in the presence of large interfering signals. In radios using some narrowband land mobile standards, interfering signals can be 70 dB greater than the desired channel, with frequency offsets as little as 25 kHz. Since these systems usually are not cellular, the geographical coverage range of mobile radios is also an important feature—they must possess excellent sensitivity to recover low-level signals originating from subscribers at the fringe of the coverage range. As a further complication, these radios are often portable with high rates of usage; they demand low power consumption using smaller, longer-lived batteries.

As an aid to equipment designers, Analog Devices has made available the AD9870 IF Digitizing Subsystem, an IC designed to meet the demanding requirements of land mobile radio, and similar narrowband radio applications, with superheterodyne architectures employing analog and/or digital modulation schemes. The AD9870 integrates the entire IF strip with minimal external components. It can accept an IF signal at frequencies as high as 300 MHz, with bandwidths up to 150 kHz, and provides a serial data output containing 16-bit I and Q data, which can then be demodulated

with a host processor. The AD9870 is intended for both base stations and subscriber units, combining the dynamic range required by base stations with the low power consumption needed by portable radios.

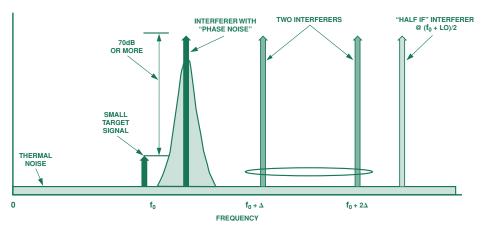

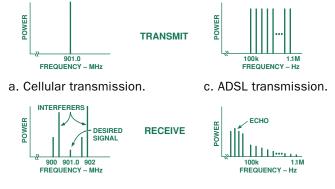

#### The big problem in all receivers is dynamic range

The dynamic range of a receiver determines its ability to recover low-level signals in the presence of larger signals, known as *blockers* and *interferers*. Figure 1 shows the various sources that can reduce the effective dynamic range of any radio receiver.

Assume for the moment that the only signal present in the spectrum is the "small target signal." The minimum detectable signal or sensitivity will be determined by the signal bandwidth (B), the receiver's detection threshold (SNR $_{MIN}$ ), the receiver's noise figure (NF), and inherent thermal noise limitations (kTB). At a temperature of 290 K, the sensitivity can be estimated with the following equation:

Sensitivity =

$$SNR_{MIN} + 10 \log(B) + NF + (-174 dBm/Hz)$$

Following are some of the potential noise sources:

Low-frequency 1/f noise becomes an issue if insufficient gain is applied to the target signal prior to down-conversion to frequencies below the 1/f corner of the process technology. DC components caused by offsets and second order distortion can also be problematic.

Large interferers can have their energy spread over a broad range of frequencies by the phase noise of the receiver's LO through a process known as "reciprocal mixing." The larger the interferer and the closer it is to the target signal, the more likely the target signal will be corrupted by the noise transfer mechanism. Also, if this interferer is large enough to induce nonlinearities in the receiver's front-end circuitry, it is possible for a spurious component to mix back into the target signal's passband. The "half-IF" problem is a specific case afflicting receivers with poor second-order linearity—in which an interferer falling halfway between the LO and the target signal generates a second order component that mixes with the LO's second harmonic to generate a spur falling on the target signal. The IIP2 specification of a receiver allows a receiver designer to quantify the "half-IF" spur. The difference, or  $\Delta$ , between the interferer level,  $P_{IN}$ , and the resulting second-order spur is IIP2 - P<sub>IN</sub>. With an IIP2 of 45 dBm, the AD9870 is mostly immune to this "half-IF" problem.

Figure 1. The "Big Problem" in all receivers is dynamic range.

Two large interferers at equally spaced frequency offsets (i.e.,  $f_0 + \Delta$  and  $f_0 + 2\Delta$ ) from the target signal will result in a spurious component falling on top of the target signal through a process of intemodulation. The linearity of a receiver in this scenario is captured in its IIP3 specification with higher numbers representing a higher tolerance to third-order intermodulation. The difference, or  $\Delta$ , between the two equal interferers,  $P_{\rm IN}$ , and the resulting third-order intermodulation component is  $2 \times ({\rm IIP3} - P_{\rm IN})$ . The AD9870 has a respectable IIP3 performance of -1 dBm, thus tolerating interferers as high as -45 dBm before degrading the receivers sensitivity.

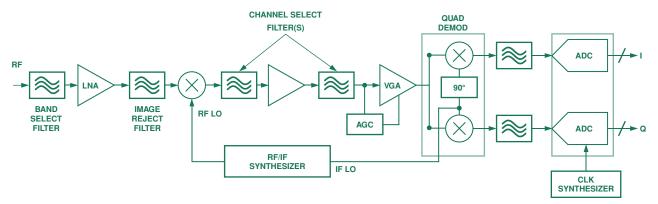

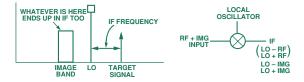

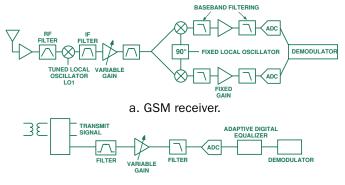

#### Superheterodyne Architecture

To cope with large interferers that would otherwise degrade the receiver's ability to recover a target low-level signal, a superheterodyne architecture is used to translate an RF signal down to one or more intermediate (IF) frequencies where filtering of the adjacent interferer signals as well as amplification and gain control of the target signal is more practical. The superheterodyne scheme has been employed since World War I and is to this day the most popular of radio receiver architectures. A generic version employing this architecture, common among narrowband digital receivers, is shown by the signal-chain in Figure 2.

Prior to RF-to-IF down-conversion, a band-select filter (duplexer) and/or image reject filter selects the entire RF band within which the target signal operates. The low-noise amplifier (LNA), which provides amplification of the intended RF band prior to downconversion, is critical in determining the receiver's sensitivity. The down-converted IF spectrum following the RF mixer often contains an array of signals of varying strengths in addition to the target signal. Channel selection and amplification occurs at IF: the target signal is selected from among the other signals via one or more crystal or SAW-type passive filters. After filtering, the target signal undergoes further amplification, with its signal strength stabilized at a preset level by an AGC loop to optimize the quadrature demodulation process. In many digital receivers, an IF analog quadrature modulator separates the IF signal into its quadrature baseband I and Q components, which are then digitized by a dual ADC. In such cases, the modulation accuracy of the demodulated signal is quite sensitive to analog offsets, quadrature LO mismatch, and I/Q gain mismatch in the quadrature modulator and dual ADC.

#### **AD9870 Architecture**

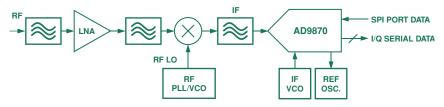

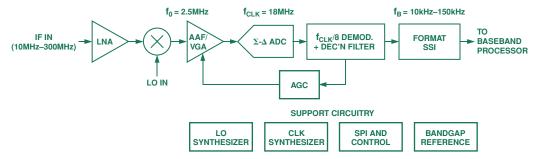

The AD9870 IF digitizing subsystem reduces the complexity of a typical superheterodyne receiver by integrating most of the IF, baseband, and some digital post processing functional blocks as shown in Figure 3.

Figure 2. Typical superheterodyne architecture for a digital receiver.

Figure 3. The AD9870 simplifies the digital receiver while enhancing performance.

Figure 4. Functional block diagram of the AD9870 shows the level of integration.

The AD9870 differs from the typical superheterodyne architecture by employing a wide-dynamic-range bandpass sigma-delta ADC to sample a second-IF signal, along with any neighboring interferers. The demodulation of the target IF signal is performed with digital accuracy and stability, while the intrusive nearby interferers can be suppressed via digital filtering.

Figure 4 shows a functional block diagram of the AD9870. Functioning similarly to the RF portion of the superheterodyne architecture, an *LNA* and mixer are used to amplify and down-convert the target signal centered at the first-IF frequency to a lower second-IF frequency suitable for digitization by the bandpass ADC.

The LNA and mixer provide approximately 10.5 dB of gain, while preserving system dynamic range with an input noise figure of 9 dB and third-order intercept of 0 dBm. The high input impedance (360  $\Omega$ ) simplifies interfacing to crystal or SAW filters. An *on-chip LO PLL synthesizer* can be used in conjunction with an external loop filter and VCO to generate a tunable LO frequency.

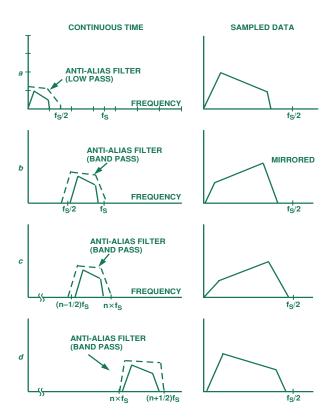

The second-IF signal is centered at exactly  $1/8^{th}$  the bandpass ADC sample rate (i.e.,  $IF2 = f_{CLK}/8$ ) to allow for a simple  $f_S/8$  digital quadrature demodulation scheme. Upon down-conversion to the second-IF, the signal is processed by a tunable (and programmable) active third-order anti-alias filter (AAF) to suppress signals which could appear within alias bands of the sampling ADC (i.e.,  $N \times f_{CLK}/8 \pm f_{CLK}/8$ ). The AAF tuning circuitry can support ADC sample rates between 13 and 18 MHz, with the 3 dB cut-off frequency typically set and tuned to slightly beyond the second-IF (i.e.,  $f_{-3dB} = f_{CLK}/3.2$ ).

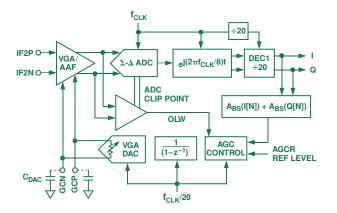

Embedded in the AAF is a variable-gain amplifier (VGA) that provides up to 26 dB of gain range (Figure 5). The VGA gain, which extends the dynamic range of the AD9870, can either be programmed directly or controlled by an automatic gain-control (AGC) loop. The AGC loop is typically invoked under strong signal conditions to prevent "overloading" or clipping of the A/D converter by maintaining a programmable fixed-signal level at the ADC input. The AD9870 implements the AGC function with a highly effective hybrid approach, as shown in Figure 5: the analog and digital domains work together in signal estimation and control.

Figure 5. A "hybrid" AGC control loop extends the dynamic range of the AD9870.

In situations where a strong target signal or interferer falls within the bandwidth of the first-stage decimate-by-20 digital filter, the signal is estimated digitally and compared to a programmed reference level (AGCR). The difference between the two levels is fed to a digital integrator, which updates a control DAC to adjust the analog voltage of the VGA. Since a strong interferer falling outside of the passband of the first-stage digital filter can not be accurately estimated, an analog loop based on a simple differential comparator monitors the input to the ADC and assumes control of the loop during any overrange condition, to reduce the VGA gain.

An external capacitor is used to "smooth" the transitions of the DAC, with a time constant established by its capacitance and the internal source resistance of the DAC. The R-C cutoff frequency is typically set well outside the control system's loop bandwidth to ensure continual digital control of the loop dynamics. The control loop bandwidth is digitally programmable with attack and decay times variable over a wide range and ability to react to any overload condition.

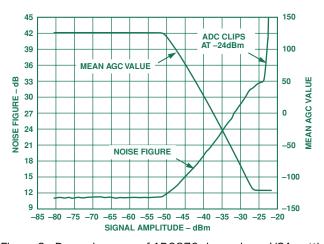

The instantaneous dynamic range of any narrowband receiver signal chain containing a VGA is dependent on the particular gain setting of the VGA, since the noise contributed by each stage in the signal path to the "overall" input-referred noise decreases as the gain of the preceding stage increases. This implies that input noise described by its noise figure, NF, is typically dominated by the first few stages (i.e., LNA and mixer); noise sources at the end of the signal chain (i.e., the ADC) have minimal effect upon the system's NF, provided that there is sufficient gain between these blocks.

Figure 6. Dynamic range of AD9870 depends on VGA setting. In the case of the AD9870, the VGA's gain is nominally adjustable over a 25 dB range. Figure 6 shows how the AD9870's noise figure is impacted by the VGA gain setting as a target signal's (or interferer's) input power is increased from –85 dBm to –23 dBm. Under small-signal conditions, the VGA is set to max gain; the AD9870's noise figure is set by the LNA/Mixer as well as the VGA's input noise. However, as the signal power is increased, a point is reached (depending on the AGC reference level) at which the VGA's gain begins to decrease to prevent ADC clipping. At this

Figure 7. Multibit fourth-order bandpass  $\Sigma$ - $\Delta$  ADC results in deep notch at  $f_{CLK}/8$ .

Figure 8. Digital quadrature demodulation, followed by programmable decimation filters, provides baseband I/Q data.

point, the VGA gain is reduced dB for dB as the signal power is further increased. Also, in this region, the input signal level to the ADC remains constant and the noise of the ADC begins to dominate such that the system's NF degrades also at a 1 dB per dB rate. As the signal power continues to increase, a point is reached (i.e., -26 dBm) at which the gain of the VGA is set to its absolute minimum and further increases in signal level are seen at the ADC input until clipping occurs (i.e., -24 dBm).

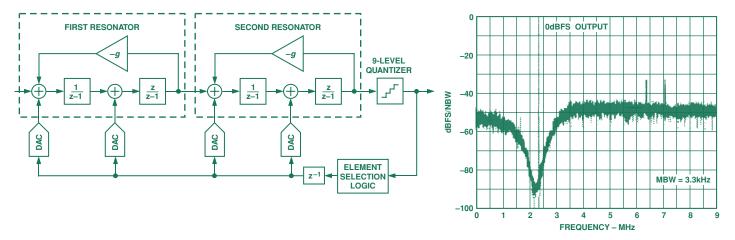

The bandpass sigma-delta ADC (Figure 7) is the "heart" of the AD9870 that makes a low second-IF digitization approach feasible and practical in an IC intended for radio systems requiring high dynamic range with minimal power consumption. This ADC, together with the back-end digital decimation filters, achieves nearly 14.5-ENOB performance within a 10-kHz bandwidth, while sampling a signal centered at frequencies as high as 2.25 MHz. It achieves these specifications while drawing a mere 13 mA from a 3.0 V power supply.

The sigma-delta ADC is based on a fourth-order switched-capacitor, multi-bit modulator consisting of two cascaded resonators that provide two complex pairs of zeros in the noise transfer function (NTF) falling near  $f_{\rm CLK}/8$ . The location of these complex zeros at the second-IF frequency, along with the multibit feedback path, help ensure a low noise floor in a narrow region ( $\pm 73.3\%$  of  $f_{\rm CLK}/8$ ) around the second-IF frequency.

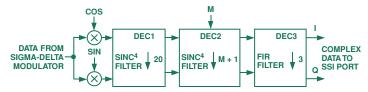

The digital output data from the ADC is fed into the digital signal processing section of the AD9870 (Figure 8). This section consists of an  $f_{\rm CLK}/8$  complex (or quadrature) demodulator followed by

three linear-phase FIR filters. The complex demodulator separates the target second-IF signal centered at  $f_{\rm CLK}/8$  into its I/Q components prior to filtering.

The output spectrum of the complex demodulator consists of the target signal, now centered at "dc," along with any undesirable interferers and/or noise not sufficiently filtered in the analog domain. A series of decimation filters are used to remove these undesirable components, while simultaneously reducing the data rate in accordance to the target channel's bandwidth. Depending on the modulation scheme, the complex data rate (hence decimation factor) is set to be at least a factor of two greater than the channel bandwidth to allow for further post-processing. Both DEC1 and DEC2 use a cascaded fourth-order comb filter topology; DEC2's decimation factor is user programmable to accommodate different channel bandwidths. DEC3 is a decimateby-3 FIR filter; it sets the close-in transition-band characteristics of the composite filter. The 16-bit I-and-Q output of DEC3 is fed into the synchronous serial-interface (SSI) function, which formats the data into a serial bit stream and embeds other optional information — AGC, signal strength, and synchronization—into the bit stream.

#### **AVAILABILITY**

The AD9870 was released to production in winter 2001. It is available in a 48-lead LQFP package for \$16.96 in 1K volume.\* The AD9870 datasheet is available on Analog Device's website (www.analog.com). An evaluation board and the associated software are also available.

<sup>\*</sup>Recommended resale price USD. Prices are subject to change without notice. For specific price quotations, get in touch with our sales offices or distributors.

## AD9873 Mixed-Signal Front End (MxFE) for Broadband Digital Set-Top Boxes

By Iuri Mehr, Joe DiPilato, and Martin Kessler

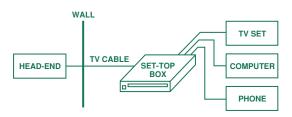

Widespread deployment of TV cable has led to extensive research in providing better quality and increased variety in TV programming and cable-modem functionality. This effort resulted in the development of digital set-top boxes from several established vendors, including Scientific Atlanta and Motorola (General Instrument). Instead of analog *vestigial-sideband* modulated (VSB) channels, digital set-top boxes receive TV programming and exchange information with the head-end station using *quadrature amplitude modulation* (QAM). Transmitting analog information in digital bits is not only more robust but also makes use of available bandwidth more efficiently. Figure 1 shows a digital set-top box connected to the head-end and to various devices inside the residence (or office).

Figure 1. Cable set-top box gateway configuration.

Several services can be unified in this fashion, including Internet access, cable TV and even phone services. High data rates allow streaming-in MPEG movies as well as high-quality telephony (voice-packet) service.

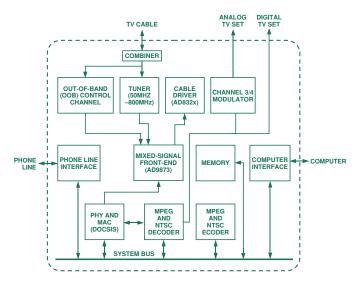

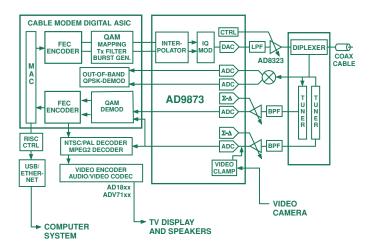

A digital set-top box, like that shown in Figure 2, comprises several major subsystems to implement such functions as a TV tuner, baseband transceivers, a channel 3/4 modulator (for compatibility with analog TV sets), MPEG and NTSC decoders and encoders, physical layer (PHY), and media access control (MAC) for cable modems. Since Internet access implies an upstream channel, a cable driver is included; it can be implemented using a member of the AD832x family. The box can also include an *out-of-band* (OOB) control channel and a phone line interface.

The multiplicity and complexity of all these blocks impose significant challenges on designers at both the component and board levels. The large amount of digital processing required, combined with the high-quality reception requirements of high-definition digital TV, pose numerous challenges to digital set-top box architects. In addition, compatibility with analog TV calls for clean analog signal processing from the wall TV cable outlet to the TV set. Therefore, selecting a proper partition for integrated functions becomes a key requirement for combining high-quality TV reception and high data rates in a cable modem at low cost.

The mixed-signal front end, which can be implemented using the AD9873, is central to the set-top box (Figure 2).

Figure 2. Inside a typical digital set-top box.

#### **Mixed-Signal Front End**

The definition of a mixed-signal front end for a set-top box must take into account the amount of functionality required from the transmit and receive data paths. Low cost is of vital importance, so selecting a proper technology is key to a successful design. In addition, time to market is equally important for both the IC vendor and the OEM. ASICs that include significant digital and analog content are often difficult to schedule due to the time needed to handle the inherent design challenges and the frequent need for customer feedback. The designers of the Analog Devices AD9873 took advantage of both their experience in set-top-box technology and their inventory of high-performance topological block core designs of the kind that would be needed to integrate the essential high-performance analog and mixed-signal functions on a single chip.

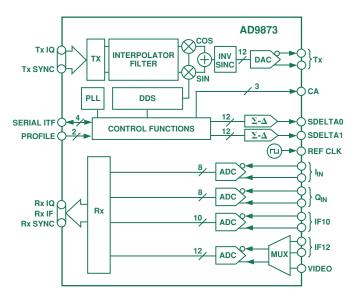

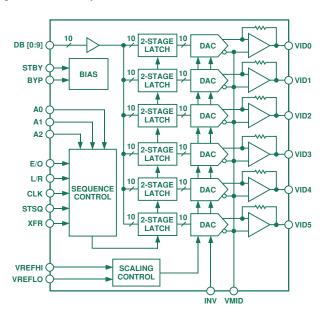

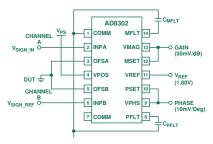

Figure 3. AD9873 functional block diagram.

Figure 3 is a block diagram of the AD9873 Analog Front End Converter for Set-Top Boxes and Cable Modems. The *receive* data path contains several analog-to-digital converters (ADCs) to accommodate the various set-top box functions described earlier. A pair of 8-bit ADCs is used to convert quadrature inputs from the demodulated OOB channel. They are designed for modest

performance—better than 7 effective number of bits (ENOB) when sampling at less than 16 MHz—since the OOB data utilizes low-complexity modulation (QPSK) in a narrow-band channel (<1 MHz). A tighter specification is required from the 10-bit ADC, due to its major role in digitizing cable modem data. This type of data is broadcast using higher-order QAM modulation, which requires a higher signal-to-noise ratio. Hence, the converter needs to exhibit better than 9 ENOB when sampling an input signal of up to 10 MHz at 33 MSPS. The fourth ADC, a 12-bit converter, sampling at 33 MHz and providing better than 10.5 ENOB for inputs up to the Nyquist rate, can digitize high-definition TV signals. For single-ended video signals multiplexed to the same input, a programmable black-level clamp is provided. The outputs of all these converters are multiplexed to reduce the number of package pins.

The transmit data path contains a demultiplexed interface, which receives I/Q baseband data, typically sampled at about 13 MHz (up to 16 MHz). Since interpolation is a powerful tool for reducing DAC output filter requirements (used successfully in the AD9772 and AD9856), three interpolation filters are used. The interpolation factor can be programmed for 12 or 16, bringing the data rate up to 230 MHz. The overall interpolator frequency response is determined by two half-band filters and a cascaded integrator comb filter (CIC). Following the interpolator, a quadrature modulator is implemented using *direct digital synthesis* (DDS) to generate the sine and cosine waveforms. Before being fed into the DAC, the signal can be compensated for the  $\sin(x)/x$  roll-off, which results from the D/A conversion process. This operation is optional, since the roll-off becomes noticeable only toward the end of the synthesized carrier frequency range. The DDS can produce a low-spurious-content complex carrier at frequencies up to approximately one-third of the sampling rate, that is, up to 70 MHz.

The ADCs are clocked directly from a low-frequency crystal; its frequency is stepped up by an on-board programmable phase-locked-loop (PLL) to provide the high-speed clock required for the DAC. This approach reduces undesirable clock jitter when sampling the ADCs and eliminates the problems and expense of an off-chip high-frequency oscillator. The programmable PLL also provides the system clock to other blocks within the set-top box. Auxiliary digital sigma-delta outputs facilitate automatic gain control or timing recovery functions. Many of the device parameters are programmable through a 3- or 4-pin serial interface.

In order to seamlessly interface with a member of the AD832x cable driver family, a separate 3-wire interface is included, and several profile registers (which can be loaded through the serial interface) are designed to speed up changes in transmit gain data and carrier frequency. This can be achieved by using dedicated external pins that address a particular profile register bank. Figure 4 shows how the AD9873 would be used in a complete digital settop box application.

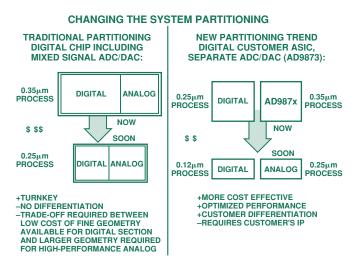

Designers of broadband modems require the combination of small form factors, high performance levels, and low cost. Because of the cost and area impact of heat management within the box, they cannot afford to dissipate watts of power in the transmit or receive path. To build the large-scale digital integrated circuits that meet these requirements in broadband modem designs, state of the art, low-voltage lithographies are needed. However, they are not

suitable for high-performance analog and mixed-signal circuitry. Products like the AD9873 provide a solution to this problem by offering the possibility of using two small highly integrated chips—a digital ASIC and a mixed-signal "everything else"—that appropriately partition the large scale digital IC from the high-performance mixed-signal component.

Figure 4. Intelligent system partitioning helps to solve the challenge of optimizing price, performance, size, and power in broadband modem designs.

Figure 5 demonstrates how this approach leads the trend in broadband communication applications away from single-chip solutions that unsuccessfully attempt to integrate the large scale digital processing with the high-performance mixed-signal devices. Emerging broadband modems require both more powerful digital processing (>MIPS) and higher performance mixed-signal (> dynamic range and bandwidth) devices. The large scale integrated digital devices used in these applications need the utmost state-of-the-art (fine geometry), low voltage, CMOS processes, while the mixed-signal devices depend on higher voltage CMOS processes that are optimized for handling mixed signals with high performance. As the first device of a new family of broadband MxFEs, the AD9873 will allow designers to take advantage of "smart partitioning."

Figure 5. Smart partitioning model.

Here's why it works: Deep submicron geometry processes do not readily support the voltage levels required by high-performance D/A and A/D converters, and coupling of digital noise into the analog signal chain will corrupt signal fidelity. There are times when trying to put everything on a single chip results in a higher-price and/or lower-performance solution. Trying to mix high-speed and wide dynamic range mixed-signal devices with very large scale digital processing is a perfect case in point. It will always require compromises either in digital area (cost), power consumption, or mixed-signal performance. The AD9873 broadband Mixed-Signal Front End, and the other MxFE products that will follow in its wake, gives designers the benefit of high integration, low cost, and low power consumption, without compromising performance.

The AD9873 applies this optimized mixed-signal technology and "smart" partitioning to provide excellent dynamic performance for a variety of modulation formats—FSK, QPSK, 16/32/64/256 QAM, OFDM, spread spectrum, etc. The digital ASIC, which includes the modulation encoding, can be implemented on the most cost effective and finest geometry possible. With this cost-effective approach, system designers can keep more "value added" in their own digital ASIC, making best use of their system expertise, proprietary algorithms, and intellectual property. The AD9873's mixed-signal partitioning resolves the cost and performance trade-off issues related to integrating mixed-signal circuits within VLSI digital ASICs by getting them off the chip.

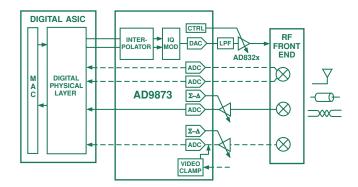

#### Other Applications for the AD9873 Mixed-Signal Front End

Besides cable set-top boxes, the AD9873 is well suited for a variety of other standard and proprietary broadband communications applications, as depicted in Figure 6. Here is a list of other applications where the AD9873 can be used:

- Cable Modem

- Digital Communications

- Data and Video Modems

- Power Line Modem

- Satellite Systems

- PC Multimedia

- Broadband Wireless Communication

- Home Networking

Figure 6. Broadband modems over cable, power line, or wireless, using the AD9873.

#### **AD9873 Key Features and Performance**

- 232 MHz Quadrature Digital Upconverter:

- DC to 70 MHz Output Bandwidth

- 12-Bit Direct IF D/A Converter

- Direct Digital Synthesis

- Interpolation and Sin(X)/X Filters

- 12-Bit 33 MSPS Direct IF ADC

- 10-Bit 33 MSPS Direct IF ADC

- Dual 8-Bit 16.5 MSPS I&Q ADCs

- Dual 12-Bit Sigma-Delta Control DACs

- Video Input with Clamp Circuitry

- Direct Interface to AD8321/AD8313 PGA Cable Driver

- Programmable PLL Clock Multiplier

- Single 3.3 V Supply Operation

- Power-Down Modes

- 100-Lead MQFP

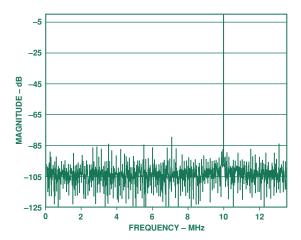

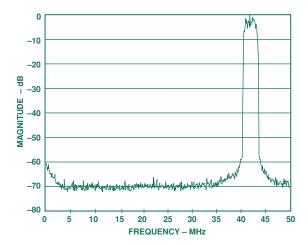

Performance of the AD9873 was characterized with respect to the commercial temperature range; however, it can be safely used from -40°C to +75°C. Figure 7 shows a spectral plot of the 12-bit ADC performance with a 10-MHz input.

Figure 7. AD9873's 12-bit ADC performance plot with 10-MHz input.

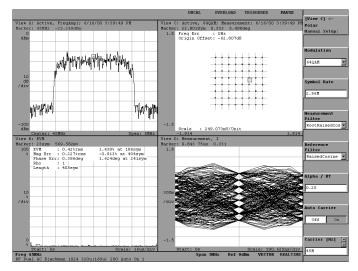

Figure 8 shows the spectral plot of the DAC producing a 42-MHz 16-QAM signal. Figure 9 shows the constellation and eye diagram of a 64-QAM signal generated by the AD9873.

Figure 8. AD9873 DAC performance plot.

Figure 9. AD9873 64-QAM constellation plot.

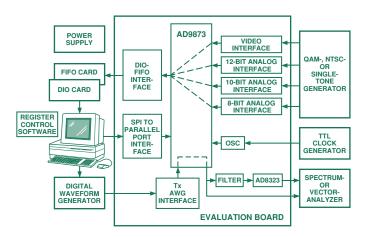

Figure 10. AD9873 evaluation setup.

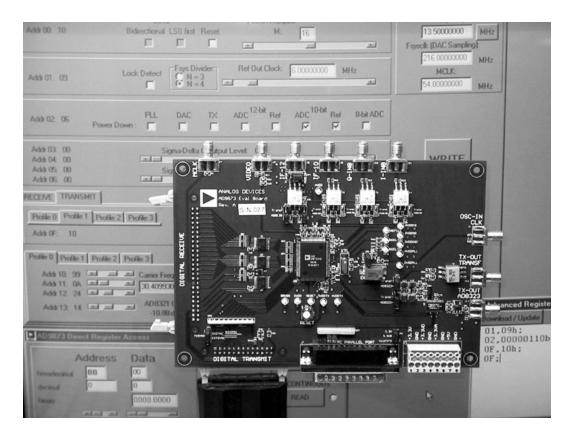

Figure 11. AD9873 evaluation board and software interface.

#### **Evaluation Board and Software**

16

The AD9873 Evaluation board and software allow users to easily program and quickly evaluate the AD9873 for a specific modem application.

#### **AVAILABILITY**

The AD9873 was released to production in summer 2000. It is available in a 100-lead MQFP package, is priced at \$16.58 (1000s), and sells for less then \$10 in high volume.

## Design a Direct 6-GHz Local Oscillator with a Wideband Integer-*N* PLL Synthesizer

By Mike Curtin (mike.curtin@analog.com)

#### INTRODUCTION

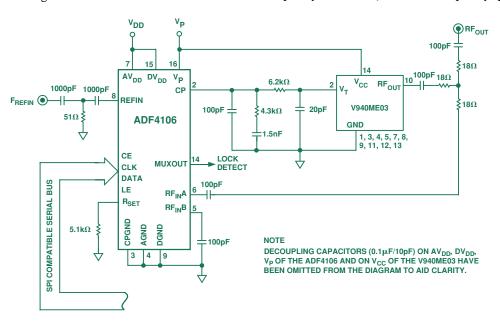

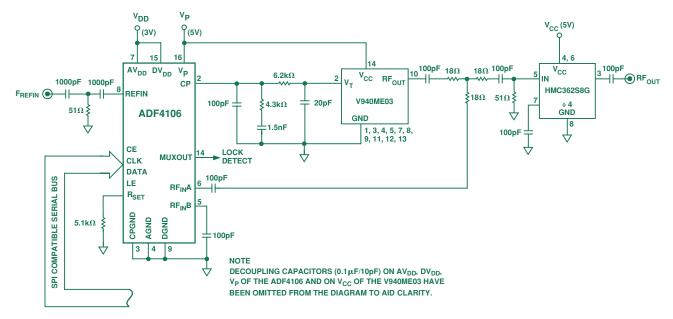

Establishing a new benchmark for speed and RF phase-noise performance, the ADF4106 Phase-Locked-Loop Synthesizer is fully specified to operate at frequencies up to 6.0 GHz. This allows designs for the 5.4-GHz to 5.8-GHz upper ISM band to be greatly simplified. Fabricated on an advanced 0.35- $\mu$ m BiCMOS process, it displaces the pin- and software-compatible 4-GHz ADF4113 as the fastest available integer-N synthesizer—and can achieve 3-dB lower phase noise to boot! It requires only a 3.3-V supply, yet its V<sub>P</sub> pin is specified at up to 5.5 V for compatibility with tuning voltage levels often required by modular VCOs used in base stations.

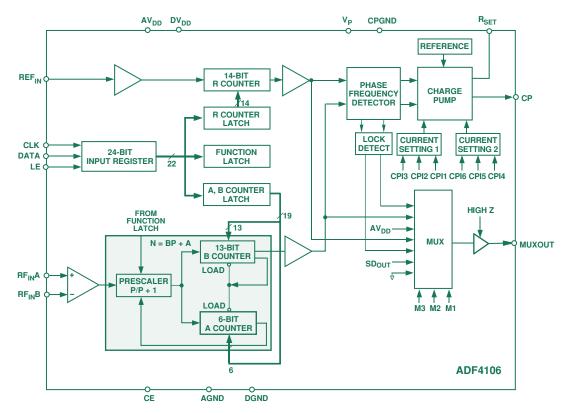

The ADF4106 frequency synthesizer (Figure 1) can be used to implement local oscillators (LOs) in the up- and down-conversion sections of wireless receivers and transmitters. It consists of a lownoise digital phase frequency detector (PFD), a precision charge pump, a programmable reference divider, programmable A and B counters, and a dual-modulus prescaler (P/P + 1). The A (6 bit) and B (13 bit) counters, in conjunction with the dual-modulus prescaler (P/P + 1), implement an N-divider (N = BP + A). In

addition, the 14-bit reference (R) counter allows selectable  $REF_{\rm IN}$  frequencies at the PFD input. A complete phase-locked loop (PLL) can be implemented if the synthesizer is used with an external loop filter and voltage-controlled oscillator (VCO). Its very high bandwidth means that frequency doublers can be eliminated in many high-frequency systems, simplifying system architecture and lowering cost.

#### Wide bandwidth allows it to function as a 6-GHz local oscillator

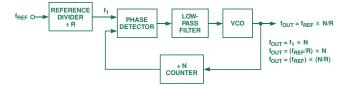

The standard PLL system architecture used by the ADF4106 and its predecessor, the ADF4113, is shown in Figure 2. Since the maximum operating frequency of the ADF4113 is about 4 GHz, higher frequencies require the use of a frequency doubler—which usually calls for an extra RF amplifier to produce an adequate level for the doubler. Use of the ADF4106 eliminates the frequency doubler and its associated circuitry, achieving a much simpler and more power-efficient LO. For example, the design shown in Figure 3 generates RF output frequencies with 1-MHz channel separation from 5.4 GHz up to 6.0 GHz. The phase noise measured at the upper end is -83 dBc/Hz.

Figure 2. Standard PLL architecture.

Because the input impedance of the ADF4106 at this high operating frequency is very close to 50  $\Omega$ , a 50- $\Omega$  terminating resistor at the RF input is not needed for maximum power transfer efficiency. When operating at lower frequencies, the *s*-parameters in the data sheet give the impedance values needed for matching.

Figure 1. Functional block diagram of the ADF4106.

### Low phase noise allows it to work as a low-noise, fast-settling 1.5-GHz local oscillator

The ADF4106, in conjunction with a wide bandwidth divider, can improve the phase noise and lock time of a standard local oscillator circuit at frequencies below 2.0 GHz.

A typical wireless system might be generating frequencies in 200-kHz increments from 1450 MHz to 1500 MHz. Using an integer-N architecture to do this, a phase/frequency detector reference frequency of 200 kHz is needed, and the N value would vary from 7250 (1450 MHz) to 7500 (1500 MHz).

Using the ADF4106 for best performance would give a phase noise figure of -88 dBc/Hz. Typical reference spurs in such a system would be -88 dBc at 200 kHz and -90 dBc at 400 kHz. Implementing a loop bandwidth of 20 kHz, typical lock time to 10 degrees of phase error would be 250  $\mu$ s.

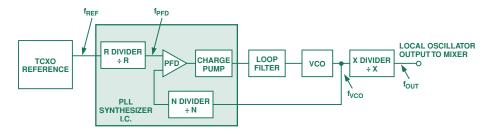

However, the wideband operation possible with the ADF4106 allows an alternative architecture to be considered, shown in Figure 4a. In this configuration, the core PLL is operated at a multiple of the final desired output frequency. In the example given above, the final desired frequency range is 1450 MHz to 1500 MHz. A multiple within the device's frequency range is 5800 MHz to 6000 MHz (four times the desired output band). In the proposed scheme, shown in Figure 4a,  $f_{\rm PFD}$  operates at 800 kHz, the  $f_{\rm VCO}$  band is 5800 MHz to 6000 MHz, and the final system LO output is obtained by dividing  $f_{\rm VCO}$  by four.

$$f_{OUT} = (f_{PFD} \times N)/X \tag{1}$$

Some consequences of using this architecture follow.

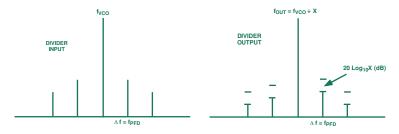

#### **Phase-noise reduction** (see page 4)

The synthesizer phase noise has a 10  $\log f_{PFD}$  relationship. This means that for every doubling of the PFD frequency, there will be 3-dB degradation in the synthesizer phase noise. However, the output from the VCO will be divided down, and its phase noise obeys a 20  $\log X$  rule. So, for every doubling of X, there will be a gain of 6 dB in phase noise performance. If the PFD frequency is quadrupled as above,  $f_{VCO}$  is divided by four to end up with the correct  $f_{OUT}$ . Thus 6 dB will be lost due to the quadrupling of  $f_{PFD}$  and 12 dB is gained due to the division by four. This results in an overall gain of 6 dB in phase-noise performance, using Figure 4a, compared to the use of the standard architecture. In this example, the resulting phase noise would be -94 dBc/Hz.

#### Reference spur reduction

In an integer-N PLL, spurious frequencies occur at integer multiples of the PFD frequency at the VCO output. In Figure 4a, using  $f_{VCO}$ , these spurs will be at  $f_{PFD}$ ,  $2f_{PFD}$ ,  $3f_{PFD}$ , etc. However, at  $f_{OUT}$ , the fundamental frequency is divided by X(X=4) but the spurious frequencies still exist at the integer multiples of the PFD frequency. Note, however, that they are reduced in amplitude by  $20 \log X$  ( $20 \log 4 = 12 \text{ dB}$ ). See Figure 4b.

So, using the architecture of Figure 4a with X = 4 and generating an  $f_{OUT}$  of 1450 MHz to 1500 MHz with 200-kHz spacing, the frequency spurs will exist at integer multiples of 800 kHz, the PFD frequency at levels below -90 dBc. Note that although the step frequency is 200 kHz, the lowest frequency spur is at 800 kHz.

Figure 3. The ADF4106 used to implement a 6.0-GHz local oscillator.

Figure 4a. Architecture for improved lock time, phase noise, and reference spurs.

Figure 4b. Comparing the output spectrum at  $f_{\text{VCO}}$  and  $f_{\text{OUT}}$  of Figure 4a.

Figure 5. Using the ADF4106 with an output divider to generate a 1.5-GHz local oscillator.

#### **Shorter lock time**

Since the PFD in Figure 4a is operating at a higher frequency, phase comparisons are occurring at a higher rate; this will cause the loop to lock faster. In addition, because of the higher PFD frequency, a wider loop bandwidth is possible, and this too helps in improving the lock time. In this example, the lock time is about 70 µs to within 10 degrees of phase error for a PLL loop bandwidth of 80 kHz.

The actual implementation of Figure 4a is shown in Figure 5.

To summarize, the circuit of Figure 5 provides the following performance:

Phase Noise -94 dBc/Hz @ 1-kHz offset

Reference Spurs <-100 dBc (system noise floor) @ 200-kHz,

400-kHz, 600-kHz offsets

-90 dBc @ 800-kHz offset

Lock Time 70 µs to within 10 degrees phase error

The price of this improved performance is the extra cost of the output divider and the extra power consumption of the system as a whole (the HMC typically adds 68 mA to the ADF4106's 13-mA current requirement). Thus improved performance must be a critical requirement for selecting this architecture. The extra board space needed for implementation is minimal since the HMC comes in an 8-lead SOIC package.

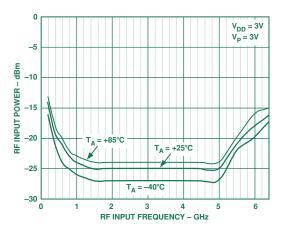

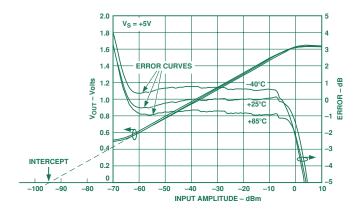

#### **BANDWIDTH**

The 0.35- $\mu$ m BiCMOS fabrication process and careful application of RF design techniques permit the prescaler section of the ADF4106 to operate at up to 6.0 GHz with an input level of -10 dBm (referred to 50  $\Omega$ ), guaranteed over the industrial temperature range (-40 to +85°C). Figure 6 shows a typical sensitivity plot for the ADF4106 in a TSSOP package at -40°C, +25°C, and +85°C. It can clearly be seen that performance to 6 GHz is well within the limits of the device with signals below -15 dBm.

Figure 6. ADF4106 sensitivity vs. frequency.

#### **PHASE NOISE**

Phase noise, a measure of the purity of the local oscillator signal, is the single most critical specification in the local oscillator section of radios—with a direct bearing on receiver sensitivity. It is the ratio to output carrier power of the noise power in a 1-Hz bandwidth at a given offset from the carrier. Expressed as a log ratio, the units of phase noise are dBc/Hz. Phase noise is typically measured with a spectrum analyzer.

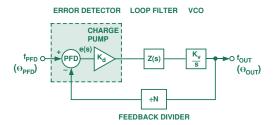

Figure 7. Basic phase-locked loop model.

The circuit of Figure 7 is used as the circuit model for the discussion of phase noise.

Total phase noise in a phase-locked loop (dB) can be expressed as follows:

$$PN_{TOTAL} = PN_{SYNTH} + 20\log N + 10\log f_{PFD}$$

(2)

where

$PN_{TOTAL}$  is the total phase noise of the PLL

$PN_{SYNTH}$  is the phase noise due to the PLL synthesizer circuit itself

20  $\log N$  is the increase of phase noise due to the frequency magnification associated with the feedback ratio, 1/N.

$10 \log f_{PFD}$  is the increase of noise associated with the incoming PFD frequency.

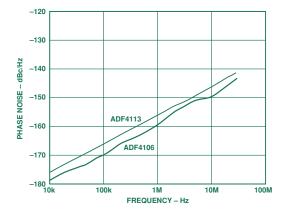

The graph in Figure 8 shows the ADF4106's phase noise characteristics as a function of PFD frequency,  $f_{PFD}$ .

With a given measured total noise, synthesizer noise can be inferred as:

$$PN_{SYNTH} = PN_{TOTAL} + 20\log N + 10\log f_{PFD} \tag{3}$$

This provides a figure of merit for the PLL Synthesizer circuit itself, irrespective of the noise contributed by PLL N value and PFD frequency, since these would be the same for any similar circuit being compared. For the ADF4106, this figure is -219 dBc/Hz, a 3-dB improvement on the ADF4113, which had been the best available integer-N synthesizer in terms of phase noise.

Figure 8. ADF4106 phase noise vs. PFD frequency.

With this phase-noise figure of merit, an engineer can work out the total PLL phase noise for any given PFD frequency and RF output frequency. For example, consider generation of a local oscillator signal with frequencies from 1700 MHz to 1800 MHz and channel spacing of 200 kHz. Using equation (2), the close-in phase noise using the ADF4106 as the PLL synthesizer is

$$PN_{TOTAL} = -219 + 20 \log(9000) + 10 \log(200 \times 10^{3})$$

$$= (-219 + 79 + 53) \, dBc/Hz$$

$$= -87 \, dBc/Hz$$

Figure 8 shows that the ADF4106 obeys the 10 logf<sub>PFD</sub> "rule" (PFD phase noise substantially linear with log frequency) fairly consistently all the way to 30 MHz. Some integer-N devices begin to degrade rapidly once the PFD frequency goes above 1 MHz.

Note that the -219 dBc/Hz figure of merit is obtained by extrapolating Figure 8 back to 1 Hz. The graph can be used to quickly identify the performance possible in a given PLL setup once the N value is known. For example, 200 kHz on the graph corresponds to phase noise of -166 dBc/Hz. Adding 20 logN (79 dBc) gives PLL phase noise of -87 dBc/Hz.

#### **ACKNOWLEDGEMENTS**

A note of thanks to Bill Hunt for valuable editorial comments, and to Brendan Daly, who verified the circuits used. The author would also like to acknowledge all the ADI customers who have provided valuable feedback on this device.

#### References

- [1]. Mini-Circuits Corporation, VCO Designer's Handbook, 1996.

- [2]. L.W. Couch, *Digital and Analog Communications Systems*. Macmillan Publishing Company, New York, 1990.

- [3]. P. Vizmuller, RF Design Guide, Artech House, 1995.

- [4]. R.L. Best, *Phase Locked Loops: Design, Simulation and Applications*, 3rd Edition, McGraw Hill, 1997.

- [5]. Bannerjee, Dean, "PLL Performance, Simulation and Design," National Semiconductor website.

- [6]. Analog Devices, Inc., ADF4106 Data Sheet. Online at www.analog.com.

- [7]. Hittite Microwave Corporation, HMC362S8G Data Sheet.

- [8] Curtin, Mike, "Phase-Locked Loops," *Analog Dialogue*, Volume 33, 1999. Three-part series in *Analog Dialogue* 33-3, 33-5, and 33-7 (1999) online at www.analog.com/publications/magazines/Dialogue/archives.html.

- [9] Goldberg, Bar-Giora, Digital Frequency Synthesis Demystified, (LLH, 1999).

- [10] Egan, William F., Frequency Synthesis by Phase Lock: 2nd Edition, John Wiley and Sons (1999).

## Winning the Battle Against Latch-up in CMOS Analog Switches

by Catherine Redmond (catherine.redmond@analog.com)

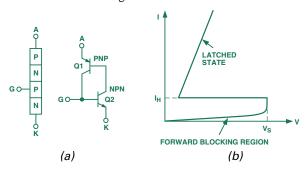

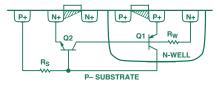

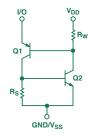

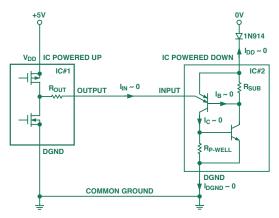

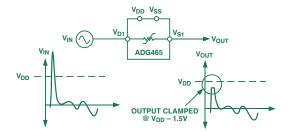

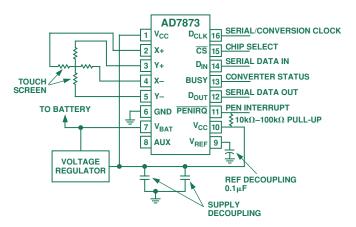

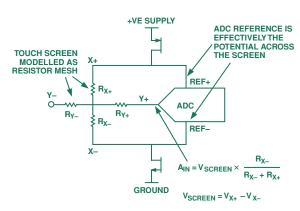

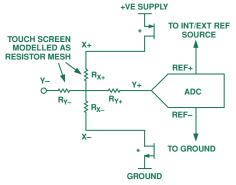

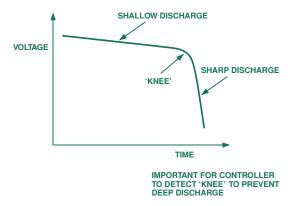

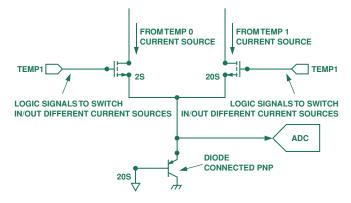

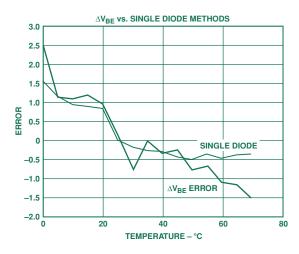

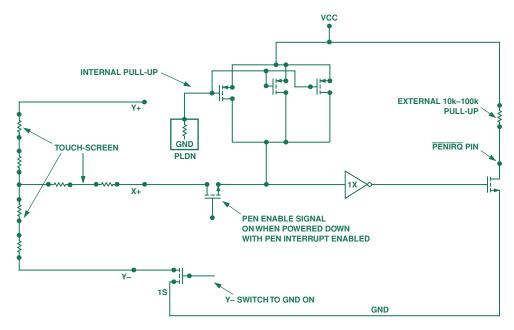

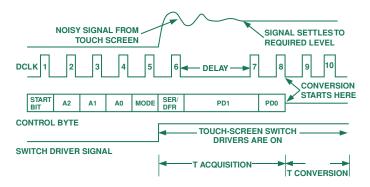

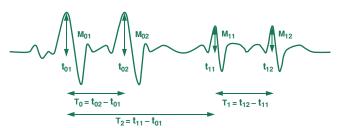

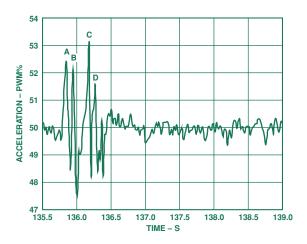

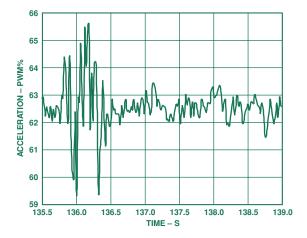

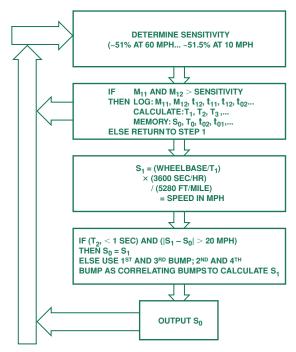

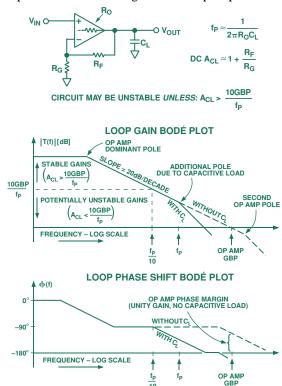

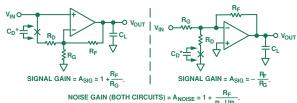

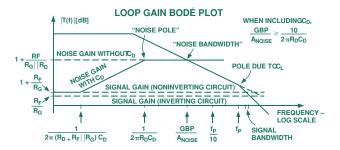

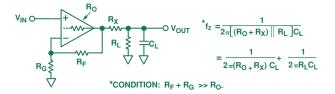

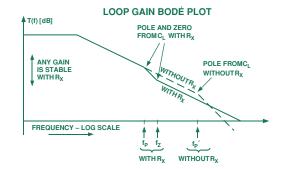

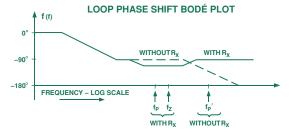

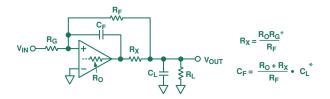

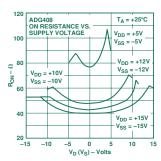

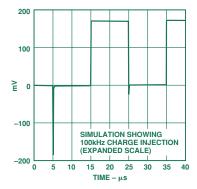

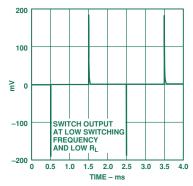

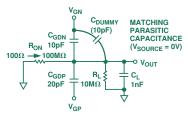

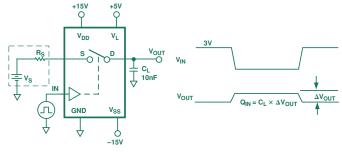

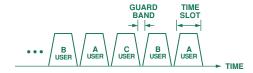

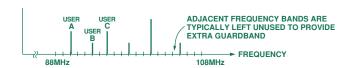

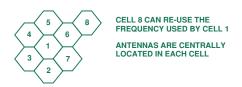

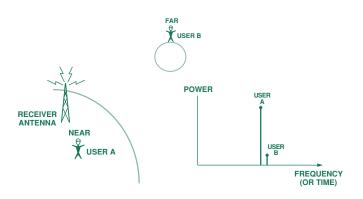

#### **INTRODUCTION**